|

| | Name | x86 |

| Designer | Intel, AMD |

| Bits | 16-bit, 32-bit, and/or 64-bit |

| Introduced | 1978 |

| Design | CISC |

| Type | Register-Memory |

| Encoding | Variable (1 to 15 bytes) |

| Branching | Status register |

| Endianness | Little |

| Page Size | 8086 - i286: None

i386, i486: 4 KB pages

P5 Pentium: added 4 MB pages

(Legacy PAE: 4 KB→2 MB)

x86-64: added 1 GB pages. |

| Extensions | x87, IA-32, P6, MMX, SSE, SSE2, x86-64, SSE3, SSSE3, SSE4, SSE5, AVX |

| Open | Partly. For some advanced features, x86 may require license from Intel; x86-64 may require an additional license from AMD. The 80486 processor has been on the market for over 20 years and so cannot be subject to patent claims. This subset of the x86 architecture is therefore fully open. |

| Gpr | 16-bit: 6 semi-dedicated registers + BP and SP;

32-bit: 6 GPRs + EBP and ESP;

64-bit: 14 GPRs + RBP and RSP. |

| Fpr | 16-bit: Optional separate x87 FPU.

32-bit: Optional separate or integrated x87 FPU, integrated SSE2 units in later processors.

64-bit: Integrated x87 and SSE2 units. |

|

|

The term x86 refers to a family of instruction set architectures based on the Intel 8086 CPU. The 8086 was launched in 1978 as a fully 16-bit extension of Intel's early 8-bit based microprocessors and also introduced segmentation to overcome the 16-bit addressing barrier of earlier chips. The term x86 derived from the fact that early successors to the 8086 also had names ending in "86". Many additions and extensions have been added to the x86 instruction set over the years, almost consistently with full backward compatibility. The architecture has been implemented in processors from Intel, Cyrix, AMD, VIA, and many others.

The term is not synonymous with IBM PC compatibility as this implies a multitude of other hardware; embedded systems as well as computers used x86 chips before the PC-compatible market started, some of them before the IBM PC itself.

As the term became common after the introduction of the 80386, it usually implies binary compatibility with the 32-bit instruction set of the 80386. This may sometimes be emphasized as x86-32 to distinguish it either from the original 16-bit "x86-16" or from the 64-bit x86-64. Although most x86 processors used in new personal computers and servers have 64-bit capabilities, to avoid compatibility problems with older computers or systems, the term x86-64 (or x64) is often used to denote 64-bit software, with the term x86 implying only 32-bit.

Although the 8086 was primarily developed for embedded systems and small single-user computers, largely as a response to the successful 8080-compatible Zilog Z80, the x86 line soon grew in features and processing power. Today, x86 is ubiquitous in both stationary and portable personal computers and has replaced midrange computers and RISC-based processors in a majority of servers and workstations as well. A large amount of software, including operating systems (OSs) such as DOS, Windows, Linux, BSD, Solaris, and Mac OS X supports x86-based hardware.

Modern x86 is relatively uncommon in embedded systems, however, and small low power applications (using tiny batteries) and low-cost microprocessor markets, such as home appliances and toys, lack any significant x86 presence. Simple 8-bit and 16-bit based architectures are common here, although VIA C7, VIA Nano, AMD's Geode, Athlon Neo, and Intel Atom are examples of 32- and 64-bit designs used in parts of these segments.

There have been several attempts, also within Intel itself, to break the market dominance of the "inelegant" x86 architecture that descended directly from the first simple 8-bit microprocessors. Examples of this are the iAPX 432 (alias Intel 8800), the Intel 960, Intel 860 and Intel and Hewlett Packard Itanium architecture. However, the continuous refinement of x86 microarchitectures, circuitry, and semiconductor manufacturing would prove it hard to replace x86 in many segments. AMD's 64 bit extension of x86 (which Intel eventually responded to with a compatible design) and the scalability of x86 chips such as the eight-core Intel Xeon and 12-core AMD Opteron is underlining x86 as an example of how continuous refinement of established industry standards can resist the competition from completely new architectures.

Note: In the following text, all instances of use of the prefixes kilo/mega/giga/tera are to be understood in the binary (powers-of-1024) sense. See the article on the IEC prefixes (kibi/mebi/gibi/tebi) for details.

|

|

|

| Generation |

First introduced |

Prominent consumer CPU brands |

Linear/physical address space |

Notable (new) features |

|---|

| 1 |

1978 |

Intel 8086, Intel 8088 and clones |

16-bit / 20-bit (segmented) |

first x86 microprocessors |

| 1982 |

Intel 80186, Intel 80188 and clones, NEC V20/V30 |

hardware for fast address calculations, fast mul/div etc. |

| 2 |

Intel 80286 and clones |

16-bit (30-bit virtual) / 24-bit (segmented) |

MMU, for protected mode and a larger address space |

| 3 (IA-32) |

1985 |

Intel 80386 and clones, AMD Am386 |

32-bit (46-bit virtual) / 32-bit |

32-bit instruction set, MMU with paging |

| 4 (FPU) |

1989 |

Intel486 and clones, AMD Am486/Am5x86 |

risc-like pipelining, integrated x87 FPU (80-bit), on-chip cache |

| 4/5 |

1997 |

IDT/Centaur-C6, Cyrix III-Samuel, VIA C3-Samuel2 / VIA C3-Ezra (2001), VIA C7 (2005) |

In-order, integrated FPU, some models with on-chip L2 cache, MMX, SSE |

| 5 |

1993 |

Pentium, Pentium MMX, Cyrix 5x86, Rise mP6 |

superscalar, 64-bit databus, faster FPU, MMX (2x 32-bit) |

| 5/6 |

1996 |

AMD K5, Nx586 (1994) |

μ-op translation, conditional move instructions |

| 6 |

1995 |

Pentium Pro, Cyrix 6x86, Cyrix MII, Cyrix III-Joshua (2000) |

as above / 36-bit physical (PAE) |

μ-op translation, conditional move instructions, Out-of-order, register renaming, speculative execution, PAE (Pentium Pro), in-package L2 cache (Pentium Pro) |

| 1997 |

AMD K6/-2/3, Pentium II/III |

L3-cache support, 3DNow, SSE (2x 64-bit) |

| 2003 |

Pentium M, Intel Core (2006) |

optimized for low power |

| 7 |

1999 |

Athlon, Athlon XP |

superscalar FPU, wide design (up to three x86 instr./clock) |

| 2000 |

Pentium 4 |

deeply pipelined, high frequency, SSE2, hyper-threading |

| 7/8 |

2000 |

Transmeta Crusoe, Efficeon |

VLIW design with x86 emulator, on-die memory controller |

| 2004 |

Pentium 4 Prescott |

64-bit / 40-bit physical in first AMD implementation. |

very deeply pipelined, very high frequency, SSE3, 64-bit capability (integer CPU) is available only in LGA 775 sockets |

| 2006 |

Intel Core 2 |

64-bit (integer CPU), low power, multi-core, lower clock frequency, SSE4 (Penryn) |

| 2008 |

VIA Nano |

Out-of-order, superscalar, 64-bit (integer CPU), hardware-based encryption, very low power, adaptive power management |

| 8 (x86-64) |

2003 |

Athlon 64, Opteron |

x86-64 instruction set (CPU main integer core), on-die memory controller, hypertransport |

| 8/9 |

2007 |

AMD Phenom |

as above / 48-bit physical for AMD Phenom |

monolithic quad-core, SSE4a, HyperTransport 3 or QuickPath, native memory controller, on-die L3 cache, modular design, in-package GPU (some Core i3/i5 models) |

| 2008 |

Intel Core i3, Intel Core i5, Intel Core i7, AMD Phenom II |

| Intel Atom |

In-order but highly pipelined, very-low-power, on some models: 64-bit (integer CPU), on-die GPU |

| 2011 |

AMD Bobcat, Llano |

Out-of-order, 64-bit (integer CPU), on-die GPU, low power (Bobcat) |

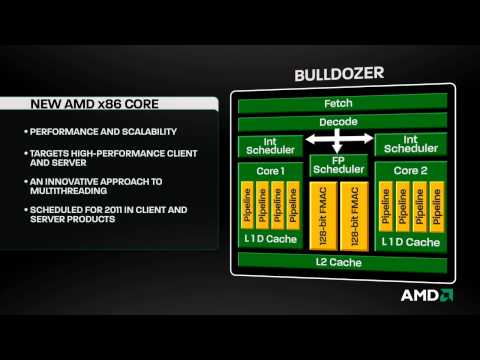

| 9 (GPU) |

2011 |

Intel Sandy Bridge, AMD Bulldozer and Trinity |

|

SSE5/AVX (4x 64-bit), highly modular design, integrated on-die GPU |

| |

2012 |

Intel Haswell |

|

FMA3 instructions, DDR4 |

| |

2012 |

Intel Larrabee |

|

very wide vector unit, LRBni instructions (8x 64-bit) |

RSS

RSS